### **General Description**

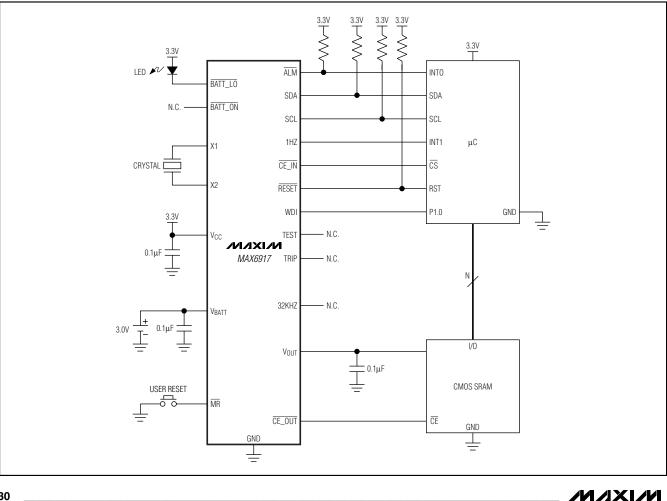

The MAX6917 provides all the features of a real-time clock (RTC) plus a microprocessor ( $\mu$ P) supervisory circuit, NV RAM controller, and backup-battery monitor function. In addition, 96 x 8 bits of static RAM are available for scratchpad storage. The MAX6917 communicates with a  $\mu$ P through an I<sup>2</sup>C<sup>†</sup>-bus-compatible serial interface.

The real-time clock/calendar provides seconds, minutes, hours, day, date, month, and year information. The end of the month date is automatically adjusted for months with fewer than 31 days, including corrections for leap years through 2099. The clock operates in either 24hr or 12hr format with an AM/PM indicator. A time/date-programmable alarm function is provided with an open-drain, active-low alarm output.

The  $\mu$ P supervisory circuit features an open-drain, active-low reset available in three different reset thresholds. A manual reset input and a watchdog function are included as well.

The NV RAM controller provides power for external SRAM from a backup battery plus chip-enable gating. The backup battery also provides data retention of the on-board 96 x 8 bits of RAM. An open-drain, active-low, battery-on signal alerts the system when operating from a battery.

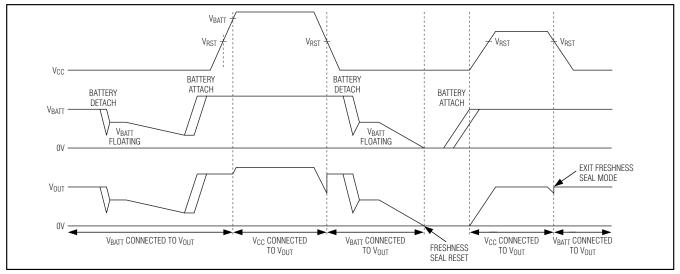

The battery-test circuitry periodically tests the backup battery for a low-battery condition. An optional external resistor network selects different battery thresholds. A freshness seal prevents battery drain until the first V<sub>CC</sub> power-up.

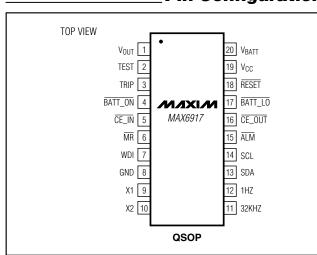

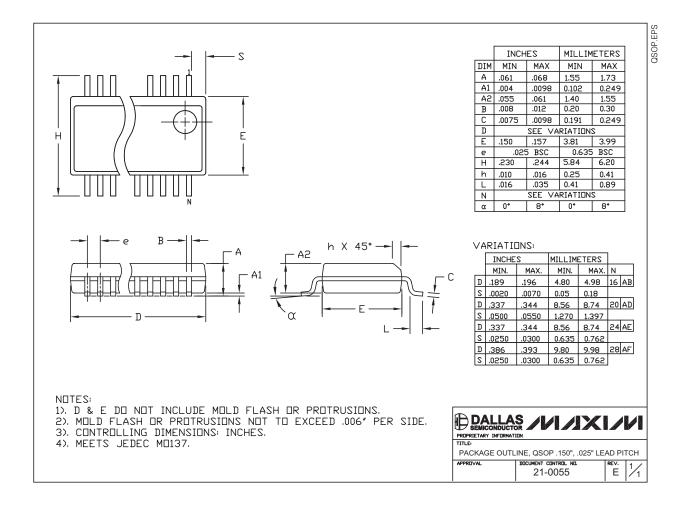

The MAX6917 has a crystal-fail-detect circuit and a data-valid bit. The MAX6917 is available in a 20-pin QSOP package and is guaranteed to operate over the extended (-40°C to +85°C) temperature range.

## Applications

Point-of-Sale Equipment

Programmable Logic Controllers

Intelligent Instruments

Fax Machines

**Digital Thermostats**

Industrial Control

# Pin Configuration and Selector Guide appear at end of data sheet.

<sup>†</sup>Purchase of I<sup>2</sup>C components from Maxim Integrated Products, Inc., or one of its sublicensed Associate Companies, conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these componenets in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

### \_\_\_Features

Real-Time Clock Counts Seconds, Minutes, Hours, Date, Month, Day of Week, and Year with Leap-Year Compensation Through 2099

- ♦ Fast (400kHz) I<sup>2</sup>C-Bus-Compatible Interface

- 96 x 8 Bits of RAM for Scratchpad Data Storage

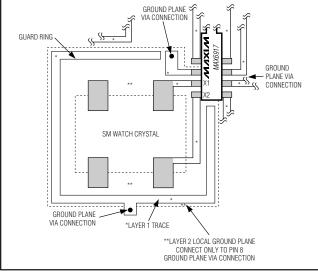

- Uses Standard 32.768kHz, 6pF Load, Watch Crystal

- Single-Byte or Multiple-Byte (Burst Mode) Data Transfer for Read or Write of Clock Registers or RAM

- Battery Monitor and Low-Battery Warning Output Internal Default for Lithium Backup-Battery Testing Pins Available for Other Backup-Battery Testing Configurations

- Dual Power-Supply Pins for Primary and Backup Power

- Battery-On Output

- NV RAM Controller

Chip-Enable Gating (Control of CE with Reset and Power Valid)

V<sub>OUT</sub> for SRAM Power

- Microprocessor Supervisor with Watchdog Input

- Programmable Time/Date Alarm Output

- Data Valid Bit (Loss of All Voltage Alerts User of Corrupt Data)

- Crystal-Fail Detect

- Reference Output Frequencies—1Hz and 32.768kHz

- Small, 20-Pin, QSOP Surface-Mount Package

## **Ordering Information**

| PART         | TEMP RANGE     | PIN-<br>PACKAGE | PKG<br>CODE |

|--------------|----------------|-----------------|-------------|

| MAX6917EO30+ | -40°C to +85°C | 20 QSOP         | E20-2       |

| MAX6917EO33+ | -40°C to +85°C | 20 QSOP         | E20-2       |

| MAX6917EO50+ | -40°C to +85°C | 20 QSOP         | E20-2       |

|              |                |                 |             |

+Denotes lead-free package.

##

Maxim Integrated Products 1

Data ters or Output

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

| VBATT, V <sub>CC</sub> to GND<br>All Other Pins to GND<br>All Other Pins to GND | 0.3V to (VCC + 0.3V) |

|---------------------------------------------------------------------------------|----------------------|

| Input Currents                                                                  |                      |

| VBATT                                                                           |                      |

| All Other Pins                                                                  | ±20mA                |

| Output Currents                                      |               |

|------------------------------------------------------|---------------|

| Vout Continuous                                      | 200mA         |

| All Other Outputs                                    | 20mA          |

| Continuous Power Dissipation                         |               |

| 20-Pin QSOP (derate 9.1mW/°C over T <sub>A</sub> = + | +70°C)727mW   |

| Operating Temperature Range                          | 40°C to +85°C |

| Junction Temperature                                 | +150°C        |

| Storage Temperature Range                            |               |

| Lead Temperature (soldering, 10s)                    | +300°C        |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = V_{CC(MIN)} \text{ to } V_{CC(MAX)}, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted}. Typical values are at T_A = +25^{\circ}\text{C}.)$  (Notes 1, 2)

| PARAMETER                                | SYMBOL | со                               | NDITIONS                      | MIN | ТҮР | МАХ  | UNITS |  |  |

|------------------------------------------|--------|----------------------------------|-------------------------------|-----|-----|------|-------|--|--|

|                                          |        | MAX6917EO30                      |                               | 2.7 | 3.0 | 3.3  |       |  |  |

| Operating Voltage Range<br>(Note 3)      | Vcc    | MAX6917EO33                      |                               | 3.0 | 3.3 | 3.6  | V     |  |  |

|                                          |        | MAX6917EO50                      |                               | 4.5 | 5.0 | 5.5  |       |  |  |

|                                          |        | MAX6917EO30                      |                               | 2.0 |     | 5.5  |       |  |  |

| Operating Voltage Range BATT<br>(Note 4) | VBATT  | MAX6917EO33                      |                               | 2.0 |     | 5.5  | V     |  |  |

|                                          |        | MAX6917EO50                      |                               | 2.0 |     | 5.5  |       |  |  |

|                                          |        | 1Hz, 32kHz                       | $V_{BATT} = 2V, V_{CC} = 0$   |     |     | 1    |       |  |  |

|                                          |        | outputs disabled;                | $V_{BATT} = 3V, V_{CC} = 0$   |     |     | 1.4  |       |  |  |

|                                          |        | XTAL FAIL                        | $V_{BATT} = 3.6V, V_{CC} = 0$ |     |     | 1.9  |       |  |  |

|                                          |        | disabled                         | $V_{BATT} = 5.5V, V_{CC} = 0$ |     |     | 3.8  |       |  |  |

|                                          |        | 1Hz, 32kHz                       | $V_{BATT} = 2V, V_{CC} = 0$   |     |     | 1.23 |       |  |  |

| Timekeeping Current VBATT                | IBATT  | outputs disabled;                | $V_{BATT} = 3V, V_{CC} = 0$   |     |     | 1.61 | μA    |  |  |

| (Note 5)                                 | IBATI  | XTAL FAIL                        | $V_{BATT} = 3.6V, V_{CC} = 0$ |     |     | 2.3  | μΑ    |  |  |

|                                          |        | enabled                          | $V_{BATT} = 5.5V, V_{CC} = 0$ |     |     | 4.08 |       |  |  |

|                                          |        | 1Hz, 32kHz                       | $V_{BATT} = 2V, V_{CC} = 0$   |     |     | 2.82 |       |  |  |

|                                          |        | enabled, outputs                 | $V_{BATT} = 3V, V_{CC} = 0$   |     |     | 4.7  |       |  |  |

|                                          |        | open; XTAL FAIL                  | $V_{BATT} = 3.6V, V_{CC} = 0$ |     |     | 6.1  |       |  |  |

|                                          |        | disabled                         | $V_{BATT} = 5.5V, V_{CC} = 0$ |     |     | 10.6 |       |  |  |

|                                          |        | 1Hz, 32kHz                       | $V_{CC} = 3.3V, V_{BATT} = 0$ |     |     | 0.1  |       |  |  |

|                                          |        | enabled, outputs open; XTAL FAIL | $V_{CC} = 3.6V, V_{BATT} = 0$ |     |     | 0.12 |       |  |  |

| Active Supply Current V <sub>CC</sub>    |        | enabled                          | $V_{CC} = 5.5V, V_{BATT} = 0$ |     |     | 0.2  |       |  |  |

| (Note 6)                                 | ICCA   | 1Hz, 32kHz                       | $V_{CC} = 3.3V, V_{BATT} = 0$ |     |     | 0.9  | mA    |  |  |

|                                          |        | outputs disabled;<br>XTAL FAIL   | $V_{CC} = 3.6V, V_{BATT} = 0$ |     |     | 0.11 |       |  |  |

|                                          |        | disabled                         | $V_{CC} = 5.5V, V_{BATT} = 0$ |     |     | 0.18 |       |  |  |

## DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = V_{CC(MIN)} \text{ to } V_{CC(MAX)}, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted}. Typical values are at T_A = +25^{\circ}\text{C}.)$  (Notes 1, 2)

| PARAMETER                                                     | SYMBOL           | СО                                                                                                                                                                                       | NDITIONS                                         | MIN                         | ТҮР                        | МАХ | UNITS |

|---------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-----------------------------|----------------------------|-----|-------|

|                                                               |                  | 1Hz, 32kHz                                                                                                                                                                               | $V_{CC} = 3.3V, V_{BATT} = 0$                    |                             |                            | 27  |       |

|                                                               |                  | enabled, outputs open; XTAL FAIL                                                                                                                                                         | $V_{CC} = 3.6V, V_{BATT} = 0$                    |                             |                            | 30  |       |

| Standby Current Vac (Nota E)                                  | loop             | enabled                                                                                                                                                                                  | $V_{CC} = 5.5V, V_{BATT} = 0$                    |                             |                            | 81  |       |

| Standby Current V <sub>CC</sub> (Note 5)                      | ICCS             | 1Hz, 32kHz                                                                                                                                                                               | $V_{CC} = 3.3V$ , $V_{BATT} = 0$                 |                             |                            | 20  | μA    |

|                                                               |                  | outputs disabled;<br>XTAL FAIL                                                                                                                                                           | $V_{CC} = 3.6V, V_{BATT} = 0$                    |                             |                            | 25  |       |

|                                                               |                  | disabled                                                                                                                                                                                 | $V_{CC} = 5.5V, V_{BATT} = 0$                    |                             |                            | 76  |       |

| Vout                                                          | 1                |                                                                                                                                                                                          |                                                  | T                           |                            |     | n     |

|                                                               |                  | $V_{CC} = 2.7V, V_{BATT}$                                                                                                                                                                | = 0, I <sub>OUT</sub> = 35mA                     | V <sub>CC</sub> -<br>0.2    |                            |     |       |

| $V_{OUT}$ in $V_{CC}$ Mode (Note 4)                           | Vout             | $V_{CC} = 3.0V, V_{BATT}$                                                                                                                                                                | = 0, I <sub>OUT</sub> = 35mA                     | V <sub>CC</sub> -<br>0.2    |                            |     | V     |

|                                                               |                  | $V_{CC} = 4.5V, V_{BATT}$                                                                                                                                                                | = 0, I <sub>OUT</sub> = 70mA                     | V <sub>CC</sub> -<br>0.2    |                            |     |       |

|                                                               |                  | $V_{BATT} = 2V, V_{CC} =$                                                                                                                                                                | 0, I <sub>OUT</sub> = 400µA                      | V <sub>BATT</sub> -<br>0.02 |                            |     |       |

| V <sub>OUT</sub> in Battery-Backup Mode<br>(Notes 4, 7)       | Vout             | V <sub>BATT</sub> = 3V, V <sub>CC</sub> =                                                                                                                                                | 0, Ι <sub>ΟUT</sub> = 800μΑ                      | V <sub>BATT</sub> -<br>0.03 |                            |     | V     |

|                                                               |                  | $V_{BATT} = 4.5V, V_{CC}$                                                                                                                                                                | = 0, I <sub>OUT</sub> = 1.5mA                    | V <sub>BATT</sub> -<br>0.05 |                            |     |       |

| V <sub>BATT</sub> -to-V <sub>CC</sub> Switchover<br>Threshold | V <sub>TRU</sub> | Power-up (V <sub>CC</sub> < V<br>to V <sub>CC</sub> (Note 7)                                                                                                                             | (RST) switch from VBATT                          |                             | V <sub>BATT</sub><br>+ 0.1 |     | V     |

| V <sub>CC</sub> -to-V <sub>BATT</sub> Switchover<br>Threshold | V <sub>TRD</sub> | Power-down (V <sub>CC</sub><br>to V <sub>BATT</sub> (Note 7)                                                                                                                             | < V <sub>RST</sub> ) switch from V <sub>CC</sub> |                             | VBATT<br>- 0.1             |     | V     |

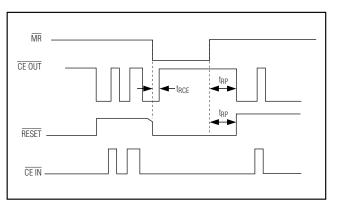

| CE_IN AND CE_OUT (Figures 10                                  | , 14, 15, 16)    |                                                                                                                                                                                          |                                                  |                             |                            |     |       |

| CE_IN Leakage Current                                         | IIL, IIH         | Disabled, V <sub>CC</sub> < V<br>V <sub>CE_IN</sub> = VCC or G                                                                                                                           |                                                  | -1                          |                            | +1  | μA    |

| CE_IN-to-CE_OUT Resistance                                    |                  | $\frac{V_{CC} = V_{CC}(MIN), V_{I}}{CE_{OUT} \text{ connecte}}$ $VIL = 0.1VCC, \overline{CE}_{-}$                                                                                        |                                                  |                             | 46                         | 140 | Ω     |

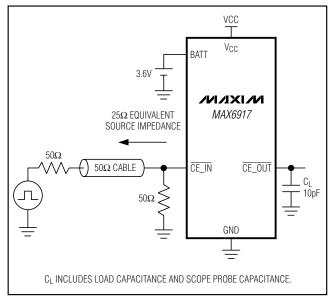

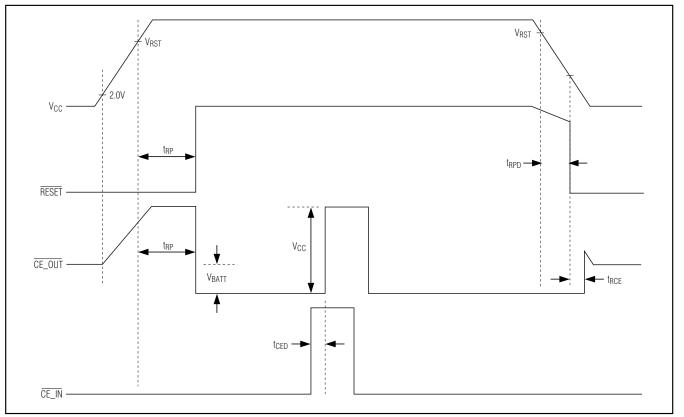

| CE_IN-to-CE_OUT Propagation<br>Delay                          | tCED             | $50\Omega$ source-imped<br>C <sub>LOAD</sub> = 10pF, V <sub>C</sub><br>V <sub>IH</sub> = 0.9V <sub>CC</sub> , V <sub>IL</sub> =<br>(Note 8); measured<br>$\overline{CE_IN}$ to the 50% μ | C = VCC(MIN),<br>= 0.1VCC<br>d from 50% point on |                             | 10                         | 20  | ns    |

| RESET Active to CE_OUT High Delay                             | <sup>t</sup> RCE | $\overline{\text{MR}}$ high to low                                                                                                                                                       |                                                  | 2                           | 10                         | 50  | μs    |

## DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = V_{CC(MIN)} \text{ to } V_{CC(MAX)}, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted}. Typical values are at T_A = +25^{\circ}\text{C}.)$  (Notes 1, 2)

| PARAMETER                                                           | SYMBOL                | CONDITIONS                                                                                     | MIN                        | TYP  | MAX  | UNITS |

|---------------------------------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------|----------------------------|------|------|-------|

| CE_OUT Active-Low Delay After<br>V <sub>CC</sub> > V <sub>RST</sub> | t <sub>RP</sub>       |                                                                                                | 140                        | 200  | 280  | ms    |

| CE_OUT High Voltage                                                 | V <sub>OH</sub>       | $I_{OH} = -100\mu$ A, V <sub>BATT</sub> = 2V, V <sub>CC</sub> = 0,<br>RESET = Iow              | 0.8 x<br>V <sub>BATT</sub> |      |      | V     |

| MR INPUT (Figure 10)                                                |                       |                                                                                                |                            |      |      |       |

|                                                                     | VIL                   |                                                                                                |                            |      | 0.8  | V     |

| MR Input Voltage                                                    | VIH                   |                                                                                                | 2.0                        |      |      | V     |

| MR Pullup Resistance                                                |                       | Internal pullup resistor                                                                       |                            | 50   |      | kΩ    |

| MR Minimum Pulse Width                                              |                       |                                                                                                | 1                          |      |      | μs    |

| MR Glitch Immunity                                                  | t <sub>GW</sub>       |                                                                                                |                            |      | 35   | ns    |

| MR to RESET Delay                                                   | t <sub>RD</sub>       | $V_{CC} = V_{CC}(MIN), V_{BATT} = 0$                                                           |                            | 450  | 600  | ns    |

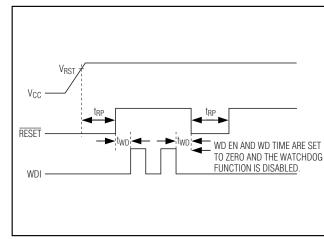

| WDI INPUT (Figure 12)                                               |                       |                                                                                                |                            |      |      |       |

| WDI Initial Timeout Period                                          |                       | V <sub>CC</sub> > V <sub>RST</sub> from rising edge of RESET                                   | 1.00                       | 1.6  | 2.25 | S     |

| Watch dog Time out Daried                                           | twdl                  | Long watchdog timeout period                                                                   | 1.00                       | 1.6  | 2.25 | S     |

| Watchdog Timeout Period                                             | twds                  | Short watchdog timeout period                                                                  | 140                        | 200  | 280  | ms    |

| Minimum WDI Input Pulse Width                                       | twDI                  |                                                                                                | 100                        |      |      | ns    |

|                                                                     | VIL                   |                                                                                                |                            |      | 0.8  | V     |

| WDI Input Threshold                                                 | VIH                   |                                                                                                | 2.0                        |      |      | V     |

| WDI Input-Leakage Current                                           |                       | $V_{WDI} = V_{CC} \text{ or } GND$                                                             | -100                       |      | +100 | nA    |

| V <sub>CC</sub> Standby Current with WDI<br>Max Frequency           | Iccsw                 | Watchdog frequency = 1MHz,<br>$V_{CC} = V_{CC(MAX)}$ , 1Hz, 32kHz outputs<br>disabled (Note 5) |                            |      | 450  | μΑ    |

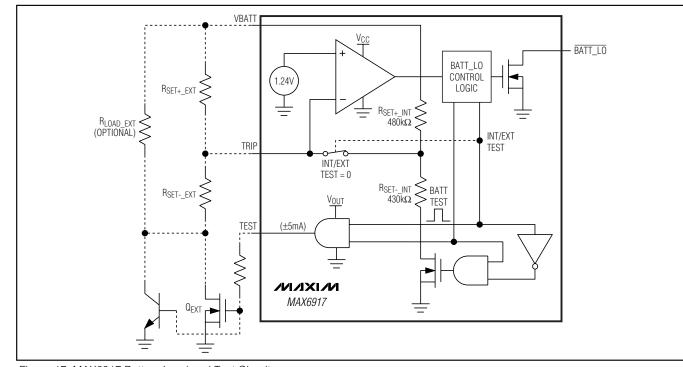

| BATTERY TEST AND TRIP (Figu                                         | res 17, 18, an        | d 19)                                                                                          |                            |      |      |       |

| VBATT Trip Point                                                    | VBTP                  | Internal mode                                                                                  | 2.45                       | 2.6  | 2.70 | V     |

| TRIP Input Threshold                                                | Vtrip                 | V <sub>CC</sub> = V <sub>CC(MAX)</sub> , V <sub>BATT</sub> = 2V,<br>external mode              | 1.14                       | 1.24 | 1.31 | V     |

| TRIP Input Comparator<br>Hysteresis                                 | VTRIP_HYST            |                                                                                                |                            | 10   |      | mV    |

| TRIP Input Current                                                  | ITRIP_LKG             | External mode                                                                                  | -100                       |      | +100 | nA    |

| Battery Test Load                                                   | RLOAD_INT             | Internal                                                                                       | 0.50                       | 0.91 | 1.30 | MΩ    |

| TEST Output-High Voltage                                            | VTEST_HIGH            | ITEST = -5mA                                                                                   | Vout -<br>0.3V             |      |      | V     |

| TEST Output-Low Voltage                                             | V <sub>TEST_LOW</sub> | I <sub>TEST</sub> = 5mA                                                                        |                            |      | 0.3  | V     |

| BATT_LO, ALM OUTPUT                                                 |                       |                                                                                                |                            |      |      |       |

|                                                                     |                       | $V_{BATT} = 2V, V_{CC} = 0, I_{OL} = 5mA$                                                      |                            |      | 0.5  |       |

| Output Low Voltage                                                  | VOL                   | $V_{CC} = 2.7V, V_{BATT} = 0, I_{OL} = 10mA$                                                   |                            |      | 0.5  | V     |

|                                                                     |                       | V <sub>CC</sub> = 4.5V, V <sub>BATT</sub> = 0, I <sub>OL</sub> = 20mA                          |                            |      | 0.5  | ]     |

| Off-Leakage                                                         | ILKG                  |                                                                                                | -100                       |      | +100 | nA    |

## DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = V_{CC(MIN)} \text{ to } V_{CC(MAX)}, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted}. Typical values are at T_A = +25^{\circ}\text{C}.)$  (Notes 1, 2)

| PARAMETER                                | SYMBOL           | CONDITION                                                                                                                         | IS          | MIN                      | ТҮР                       | MAX                      | UNITS |

|------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------|--------------------------|---------------------------|--------------------------|-------|

| BATT_ON OUTPUT                           |                  |                                                                                                                                   |             |                          |                           |                          |       |

|                                          |                  | $V_{BATT} = 2V, V_{CC} = 0, I_{OL} =$                                                                                             | 5mA         |                          |                           | 0.5                      |       |

| Output Low Voltage                       | Vol              | $V_{BATT} = 2.7V, V_{CC} = 0, I_{OL}$                                                                                             | = 10mA      |                          |                           | 0.5                      | V     |

|                                          |                  | $V_{BATT} = 4.5V, V_{CC} = 0, I_{OL}$                                                                                             | = 20mA      |                          |                           | 0.5                      |       |

| Off-Leakage                              | I <sub>LKG</sub> |                                                                                                                                   |             | -100                     |                           | +100                     | nA    |

| RESET                                    |                  |                                                                                                                                   |             |                          |                           |                          |       |

|                                          |                  | MAX6917EO30                                                                                                                       |             | 2.5                      | 2.63                      | 2.7                      |       |

| RESET Threshold Voltage                  | VRST             | MAX6917EO33                                                                                                                       |             | 2.8                      | 2.93                      | 3.0                      | V     |

|                                          |                  | MAX6917EO50                                                                                                                       |             | 4.1                      | 4.38                      | 4.5                      |       |

| V <sub>RST</sub> Hysteresis              | VHYST            |                                                                                                                                   |             |                          | 30                        |                          | mV    |

|                                          |                  | V <sub>CC</sub> falling from V <sub>RST(MAX)</sub>                                                                                | MAX6917EO30 |                          | 27                        | 75                       |       |

| V <sub>CC</sub> Falling-Reset Delay      | trpd             | to $V_{RST(MIN)}$ , measured from the beginning of $V_{CC}$                                                                       | MAX6917EO33 |                          | 37                        | 90                       | μs    |

|                                          |                  | falling to RESET low                                                                                                              | MAX6917EO50 |                          | 50                        | 120                      |       |

| Main Reset Active-Timeout Period         | t <sub>RP</sub>  |                                                                                                                                   |             | 140                      | 200                       | 280                      | ms    |

| RESET Output Voltage                     | V <sub>OL</sub>  | $\label{eq:RESET} \overrightarrow{\text{RESET}} \text{ asserted, } I_{OL} = 1.6 \text{mA, } V_{BATT} = 2 \text{V}, \\ V_{CC} = 0$ |             |                          |                           | 0.2                      | V     |

| Off-Leakage                              | I <sub>LKG</sub> |                                                                                                                                   |             | -100                     |                           | +100                     | nA    |

| I <sup>2</sup> C DIGITAL INPUTS SCL, SDA |                  |                                                                                                                                   |             |                          |                           |                          |       |

| Input High Voltage                       | VIH              |                                                                                                                                   |             | 0.7 x<br>V <sub>CC</sub> |                           |                          | V     |

| Input Low Voltage                        | V <sub>IL</sub>  |                                                                                                                                   |             |                          |                           | 0.3 x<br>V <sub>CC</sub> | V     |

| Input Hysteresis                         | V <sub>HYS</sub> |                                                                                                                                   |             |                          | 0.05 x<br>V <sub>CC</sub> |                          | V     |

| Input Leakage Current                    |                  | $V_{IN} = 0$ to $V_{CC}$                                                                                                          |             | -100                     |                           | +100                     | nA    |

| Input Capacitance                        |                  | (Note 8)                                                                                                                          |             |                          |                           | 10                       | рF    |

| SDA Output Low Voltage                   | Vol              | $I_{OL} = 4mA$ , $V_{CC} = V_{CC}(MIN)$                                                                                           |             |                          |                           | 0.4                      | V     |

| FREQUENCY OUTPUTS (32kHz a               | and 1Hz)         |                                                                                                                                   |             |                          |                           |                          |       |

|                                          |                  | $V_{CC} = 0$ , $V_{BATT} = 2V$ ,<br>$I_{OL} = 100\mu A$                                                                           |             |                          |                           | 0.2                      |       |

| 32kHz and 1Hz<br>OUT Low Voltage         | Vol              | $V_{CC} = 2.7V, V_{BATT} = 0,$<br>$I_{OL} = 1mA$                                                                                  |             |                          |                           | 0.4                      | V     |

|                                          |                  | $V_{CC} = 4.5V, V_{BATT} = 0,$<br>$I_{OL} = 2mA$                                                                                  |             |                          |                           | 0.5                      |       |

## DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = V_{CC(MIN)} \text{ to } V_{CC(MAX)}, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted}. Typical values are at T_A = +25^{\circ}\text{C}.)$  (Notes 1, 2)

| PARAMETER                         | SYMBOL          | CONDITIONS                                                | MIN                        | TYP | MAX | UNITS |

|-----------------------------------|-----------------|-----------------------------------------------------------|----------------------------|-----|-----|-------|

|                                   |                 | $V_{CC} = 0$ , $V_{BATT} = 2V$ ,<br>$I_{OH} = -100 \mu A$ | Vout -<br>0.1V             |     |     |       |

| 32kHz and 1Hz<br>OUT High Voltage | V <sub>OH</sub> | $V_{CC} = 2.7V, V_{BATT} = 0,$<br>$I_{OH} = -1mA$         | V <sub>OUT</sub> -<br>0.3V |     |     | V     |

|                                   |                 | $V_{CC} = 4.5V, V_{BATT} = 0,$<br>$I_{OH} = -2mA$         | V <sub>OUT</sub> -<br>0.4V |     |     |       |

## AC ELECTRICAL CHARACTERISTICS

$(V_{CC} = V_{CC(MIN)}$  to  $V_{CC(MAX)}$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 2)

| PARAMETER                                       | SYMBOL              | CONDITIONS                                      | MIN              | ТҮР | MAX     | UNITS |

|-------------------------------------------------|---------------------|-------------------------------------------------|------------------|-----|---------|-------|

| FAST I <sup>2</sup> C-BUS TIMING (Figure 2      | (Note 9))           |                                                 |                  |     |         |       |

| SCL Clock Frequency                             | fSCL                | (Note 10)                                       | 800              |     | 400,000 | Hz    |

| Bus Timeout                                     | <b>TIMEOUT</b>      |                                                 | 1                |     | 2       | S     |

| Bus Free Time Between STOP and START Conditions | t <sub>BUF</sub>    |                                                 | 1.3              |     |         | μs    |

| Hold Time After (Repeated)<br>START Conditions  | <sup>t</sup> HD:STA | After this period, the first clock is generated | 0.6              |     |         | μs    |

| Repeated START Condition<br>Setup Time          | <sup>t</sup> HD:STA |                                                 | 0.6              |     |         | μs    |

| STOP Condition Setup Time                       | tsu:sto             |                                                 | 0.6              |     |         | μs    |

| Data Hold Time                                  | thd:dat             | (Notes 11, 14)                                  | 0                |     | 0.9     | μs    |

| Data Setup Time                                 | tsu:dat             |                                                 | 100              |     |         | ns    |

| SCL Low Period                                  | tLOW                |                                                 | 1.3              |     |         | μs    |

| SCL High Period                                 | thigh               |                                                 | 0.6              |     |         | μs    |

| SCL/SDA Rise Time (Receiving)                   | t <sub>R</sub>      | (Note 12)                                       | 20 +<br>0.1 × Cb |     | 300     | ns    |

| SCL/SDA Fall Time (Receiving)                   | tF                  | (Notes 12, 13)                                  | 20 +<br>0.1 × Cb |     | 300     | ns    |

| SCL/SDA Fall Time (Transmitting)                | tF                  | (Notes 12, 13)                                  | 20 +<br>0.1 × Cb |     | 250     | ns    |

| Pulse Width of Spike Suppressed                 | tsp                 |                                                 | 0                |     | 50      | ns    |

| Capacitive Load for Each Bus<br>Line            | Cb                  |                                                 |                  |     | 400     | pF    |

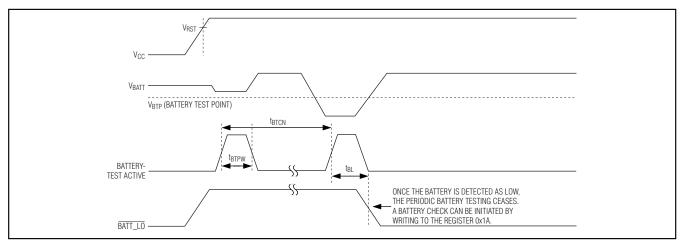

| BATTERY-TEST TIMING (Figure                     | 18)                 | · · · · · · · · · · · · · · · · · · ·           |                  |     |         |       |

| Battery Test to BATT_LO Active                  | t <sub>BL</sub>     | (Note 8)                                        |                  |     | 1       | S     |

| Battery-Test Cycle—Normal                       | <b>t</b> BTCN       | (Note 8)                                        |                  | 24  |         | hr    |

| Battery-Test Pulse Width                        | <b>t</b> BTPW       | (Note 8)                                        |                  |     | 1       | S     |

Note 1:  $V_{RST}$  is the reset threshold for  $V_{CC}$ . See the Selector Guide section.

Note 2: All parameters are 100% tested at  $T_A = +85^{\circ}C$ . Limits overtemperature are guaranteed by design and are not production tested.

### AC ELECTRICAL CHARACTERISTICS (continued)

(V<sub>CC</sub> = V<sub>CC(MIN)</sub> to V<sub>CC(MAX)</sub>, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 2)

- **Note 3:** I<sup>2</sup>C serial interface is operational for V<sub>CC</sub> > V<sub>RST</sub>.

- Note 4: See the Detailed Description section (VOUT function).

- **Note 5:**  $I_{BATT}$  is specified with SDA = SCL =  $V_{CC}$ ,  $\overline{CE_{IN}} = WDI = GND$ ,  $V_{OUT}$ ,  $\overline{CE_{OUT}}$ , and  $\overline{MR}$  floating.  $I_{CCS}$  is specified with SDA = SCL =  $V_{CC}$ ,  $\overline{CE_{IN}} = WDI = GND$ ,  $V_{OUT}$ ,  $\overline{CE_{OUT}}$ , and  $\overline{MR}$  floating.

- Note 6: I<sup>2</sup>C serial interface operating at 400kHz, SDA pulled high, and WDI = V<sub>CC</sub> or GND, V<sub>OUT</sub> and CE\_OUT floating.

- Note 7: For OUT switchover to BATT, VCC must fall below VRST and VBATT. For OUT switchover to VCC, VCC must be above VRST or above VBATT.

- Note 8: Guaranteed by design. Not subject to production testing.

- **Note 9:** All values are referred to V<sub>IH (MIN)</sub> and V<sub>IL(MAX)</sub> levels.

- Note 10: Minimum SCL clock frequency is limited by the MAX6917 bus timeout feature, which resets the serial bus interface if either SDA or SCL is held low for 1s to 2s. When using the burst read or write command, all 96 bytes of RAM must be read/written within the timeout period. See the *Timeout Feature* section.

- Note 11: A device must internally provide a hold time of at least 300ns for the SDA signal (referred to the V<sub>IH(MIN)</sub> of the SCL signal) to bridge the undefined region of the falling edge of SCL.

- Note 12: Cb is the total capacitance of one bus line in pF.

- **Note 13:** The maximum t<sub>F</sub> for the SDA and SCL bus lines is specified at 300ns. The maximum fall time for the SDA output stage t<sub>F</sub> is specified at 250ns. This allows series-protection resistors to be connected between the SDA/SCL pins and the SDA/SCL bus lines without exceeding the maximum specified t<sub>F</sub>.

- Note 14: The maximum tHD:DAT only has to be met if the device does not stretch the LOW period (tLOW) of the SCL signal.

### \_Typical Operating Characteristics

MIXI/M

0

0.4

0.8

1.2

OUTPUT CURRENT (mA)

1.6

2.0 2.4

## **Typical Operating Characteristics (continued)**

M/X/M

## Pin Description

| PIN | NAME    | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Vout    | Supply Output for External SRAM or Other ICs Requiring Use of Backup-Battery Power. When $V_{CC}$ rises above the reset threshold or above $V_{BATT}$ , $V_{OUT}$ is connected to $V_{CC}$ . When $V_{CC}$ falls below $V_{RESET}$ and $V_{BATT}$ , $V_{BATT}$ is connected to $V_{OUT}$ . Connect a 0.1µF low-leakage bypass capacitor from $V_{OUT}$ to GND. Leave open if not used.                                                                                                                                                      |

| 2   | TEST    | External Battery Test. Active high for 1s during each battery test. Intended to drive an external MOSFET or bipolar transistor for an external battery-test configuration. External test must be selected in the control register to use TEST; otherwise, it remains low. Leave open if not used.                                                                                                                                                                                                                                           |

| 3   | TRIP    | External Trip Set. If a different battery-low threshold is desired other than the internal POR default of $V_{BTP}$ , then connect $R_{SET+}$ between $V_{BATT}$ and TRIP and $R_{SET-}$ between TRIP and the drain or collector of an external transistor whose base or gate is connected to TEST; Figure 17 (see the <i>Battery Test</i> section). External test must be selected in the control register to use TRIP. Leave open if not used.                                                                                            |

| 4   | BATT_ON | Open-Drain Battery-On Indicator. BATT_ON is active low when the MAX6917 is powered from VBATT.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5   | CE_IN   | Chip-Enable Input. The input to the chip-enable gating circuitry. Connect CE_IN to GND if unused.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6   | MR      | Manual-Reset Input. A logic low on $\overline{\text{MR}}$ asserts $\overline{\text{RESET}}$ . $\overline{\text{RESET}}$ remains asserted as long as $\overline{\text{MR}}$ is low and for t <sub>RP</sub> after $\overline{\text{MR}}$ returns high. The active-low $\overline{\text{MR}}$ input has an internal pullup resistor. $\overline{\text{MR}}$ can be driven from a TTL or CMOS-logic line or shorted to ground with a switch. Internal debouncing circuitry ensures noise immunity. Leave $\overline{\text{MR}}$ open if unused. |

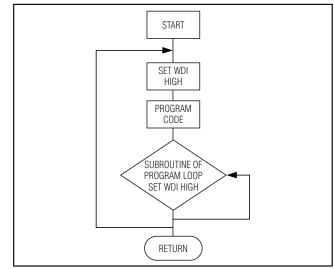

| 7   | WDI     | Watchdog Input. If WDI remains either high or low for longer than the watchdog timeout period, the internal watchdog timer runs out and RESET is asserted. The internal watchdog timer clears while RESET is asserted or when WDI sees a rising or falling edge. The watchdog function can be disabled from the control register. The timeout period is configurable in the control register for 200ms or 1.6s.                                                                                                                             |

| 8   | GND     | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

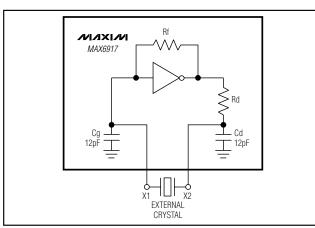

| 9   | X1      | 32.768kHz Crystal-Oscillator Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 10  | X2      | 32.768kHz Crystal-Oscillator Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

## Pin Description (continued)

| PIN | NAME    | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11  | 32KHZ   | 32.768kHz Output. Buffered push-pull output that is enabled from the FOUT configuration register.                                                                                                                                                                                                                                                                                                                                                                                                     |

| 12  | 1HZ     | 1Hz Output. Buffered push-pull output that is enabled from the FOUT configuration register.                                                                                                                                                                                                                                                                                                                                                                                                           |

| 13  | SDA     | Open-Drain Data Input/Output. I <sup>2</sup> C bus serial data input/output connection.                                                                                                                                                                                                                                                                                                                                                                                                               |

| 14  | SCL     | Serial Clock Input. I <sup>2</sup> C bus clock for input/output data transfers.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 15  | ALM     | Open-Drain, Active-Low Alarm Output. ALM goes low when RTC time matches alarm thresholds set in the alarm threshold registers. ALM stays low until cleared by reading or writing to the alarm configuration register or to any of the alarm threshold registers.                                                                                                                                                                                                                                      |

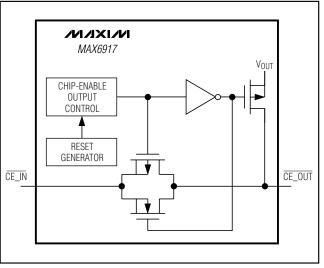

| 16  | CE_OUT  | Chip-Enable Output. $\overline{CE}_{OUT}$ goes low only when $\overline{CE}_{IN}$ is low and $\overline{RESET}$ is not asserted. If $\overline{CE}_{IN}$ is low when $\overline{RESET}$ is asserted, $\overline{CE}_{OUT}$ remains low for t <sub>RCE</sub> or until $\overline{CE}_{IN}$ goes high, whichever occurs first. $\overline{CE}_{OUT}$ is pulled to V <sub>OUT</sub> .                                                                                                                    |

| 17  | BATT_LO | Open-Drain, Battery-Low Indicator. $\overrightarrow{BATT\_LO}$ is active low when the V <sub>BATT</sub> input is tested below V <sub>BTP</sub> if the internal trip is selected in the control register (POR default). If external trip is selected in the control register, then $\overrightarrow{BATT\_LO}$ is active low when TRIP is less than V <sub>TRIP</sub> .                                                                                                                                |

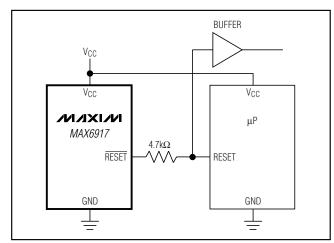

| 18  | RESET   | Open-Drain, Active-Low Reset Output. $\overline{\text{RESET}}$ pulses low for t <sub>RP</sub> when triggered, and stays low whenever V <sub>CC</sub> is below the reset threshold or when MR is logic low. RESET remains low for t <sub>RP</sub> after either V <sub>CC</sub> rises above the reset threshold or MR goes from low to high.                                                                                                                                                            |

| 19  | Vcc     | Main Supply Input. Connect a $0.1\mu$ F bypass capacitor from V <sub>CC</sub> to GND.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 20  | VBATT   | Backup-Battery Input. When V <sub>CC</sub> falls below the reset threshold and V <sub>BATT</sub> , V <sub>OUT</sub> switches from V <sub>CC</sub> to V <sub>BATT</sub> . When V <sub>CC</sub> rises above V <sub>BATT</sub> or the reset threshold, V <sub>OUT</sub> reconnects to V <sub>CC</sub> . V <sub>BATT</sub> may exceed V <sub>CC</sub> . Connect V <sub>BATT</sub> to GND if no backup-battery supply is used. Connect a 0.1µF low-leakage bypass capacitor from V <sub>BATT</sub> to GND. |

## **Detailed Description**

### **Functional Description**

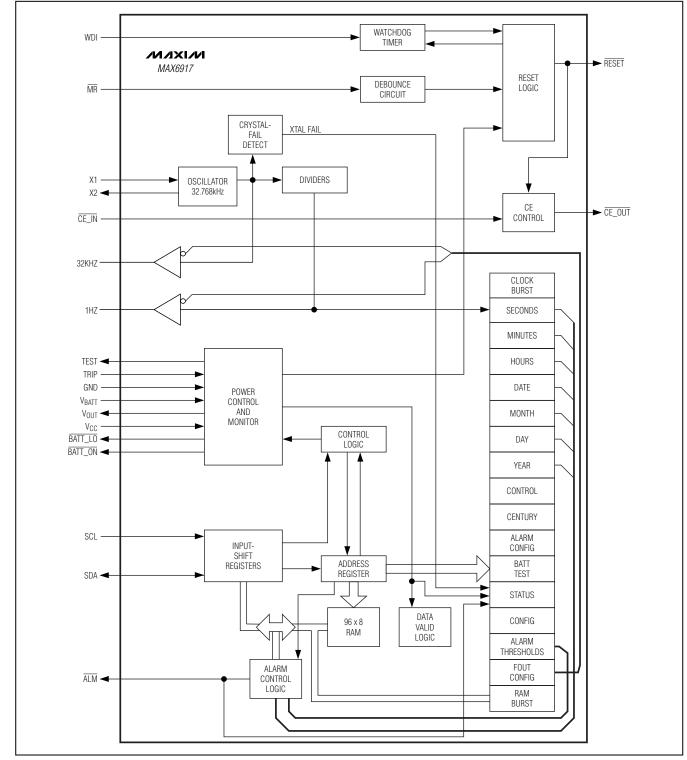

The MAX6917 contains eight 8-bit timekeeping registers, seven 8-bit alarm threshold registers, one status register, one control register, one alarm-configuration register, and 96 x 8 bits of SRAM. In addition to single-byte reads and writes to registers and RAM, there is a burst timekeeping register read/write command, a burst RAM read/write command, and a battery-test command that allows software-commanded testing of the backup battery at any time. An I<sup>2</sup>C-bus-compatible interface allows serial communication with a  $\mu P$ . When V<sub>CC</sub> is less than the reset threshold, the serial interface is disabled to prevent erroneous data from being written to the MAX6917. A µP supervisory section and an NVRAM controller are provided for ease of implementation with µP-based systems. A crystal fail-detect circuit and a data-valid bit can be used to guarantee RAM data integrity and valid timekeeping data. Two reference frequencies outputs, 32.768kHz and 1Hz, are provided for external device clocking. Time and calendar data are stored in a binary-coded decimal (BCD) format. Figure 1 shows the functional diagram of the MAX6917.

**Real-Time Clock** The RTC provides seconds, minutes, hours, day, date, month, and year information. The end of the months is automatically adjusted for months with fewer than 31 days, including corrections for leap years through 2099.

### **Crystal Oscillator**

The MAX6917 uses an external, standard 6pF load watch crystal. No other external components are required for this timekeeping oscillator. Power-up oscillator start time is dependent mainly upon applied  $V_{CC}$  and ambient temperature. The MAX6917, because of its low timekeeping current, exhibits a typical startup time of 1s to 2s.

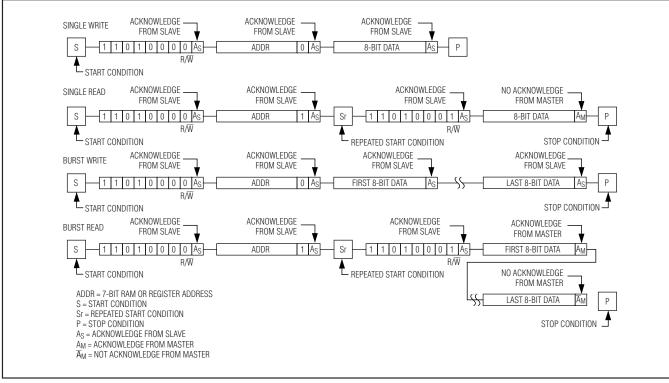

### I<sup>2</sup>C-Compatible Interface

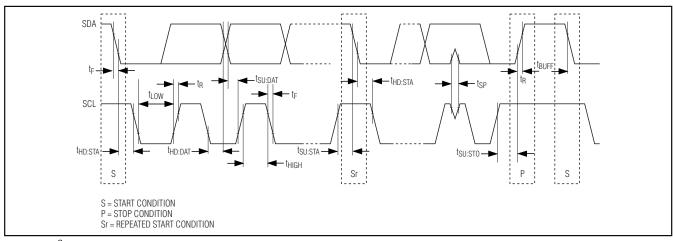

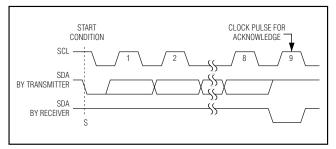

The I<sup>2</sup>C bus allows bidirectional, 2-wire communication between different ICs. The two lines are serial data line (SDA) and serial clock line (SCL). Both lines must be connected to a positive supply through individual pullup resistors (see the *Typical Application Circuit*). Data transfer can only be initiated when the bus is not busy (both SDA and SCL are high). Figure 2 shows a timing diagram for I<sup>2</sup>C communication.

Figure 1. Functional Diagram

Figure 2. I<sup>2</sup>C Communication Timing Diagram

To maximize battery life and prevent erroneous data from being entered into the MAX6917, the serial bus interface is disabled when V<sub>CC</sub> is below V<sub>RST</sub>. If the SDA or SCL serial interface lines are held low for longer than 1s to 2s, the serial bus interface resets and awaits for a new START condition (see the *START and STOP Conditions* section).

#### I<sup>2</sup>C System Configuration

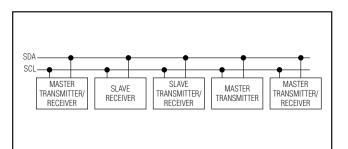

A device on the I<sup>2</sup>C-compatible bus that generates a message is called a transmitter and a device that receives the message is called a receiver. The device that controls the message is the master and the devices that are controlled by the master are called slaves (Figure 3). The word message refers to data in the form of three 8-bit bytes for a single read or write. The first byte is the slave ID byte, the second byte is the address/command byte, and the third is the data.

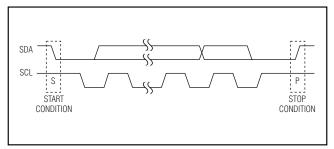

#### START and STOP Conditions

Data transfer can only be initiated when the bus is not busy (both SDA and SCL are high). A high-to-low transition of SDA while SCL is high defines a START (S) condition; low-to-high transition of SDA while SCL is high defines a STOP (P) condition (Figures 2, 4). Any time a START condition occurs, the slave ID must follow immediately, regardless of completion of a previous data transfer.

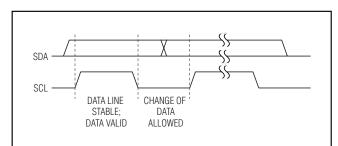

After the START condition occurs, 1 bit of data is transferred for each clock pulse. The data on SDA must remain stable during the high portion of the clock pulse as changes in data during this time are interpreted as a control signal (Figure 5).

#### Bit Transfer

#### Acknowledge

The acknowledge bit is a clocked 9th bit that the recipient uses to handshake receipt of each byte of data (Figure 6). Thus, each byte transferred effectively requires 9 bits. The master generates the 9th clock pulse, and the recipient pulls down SDA during the acknowledge clock pulse, such that the SDA line is stable low during the high portion of the clock pulse. A master receiver must signal an end of data to the transmitter by not generating an acknowledge on the last byte that has been clocked out of the slave. In this case, the transmitter must leave the SDA high to enable the master to generate a STOP condition. If a STOP condition is received before the current byte of data transfer is completed in burst mode, the last incomplete byte is ignored if it is a burst transaction to RAM or the whole burst transaction is ignored if it is a burst transaction to the timekeeping registers. There is no limit to the number of bytes that can be transmitted between a START and a STOP condition.

#### Slave Address

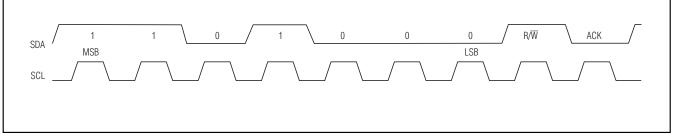

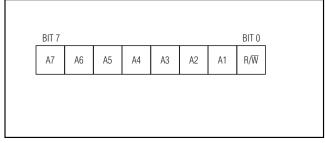

Before any data is transmitted on the I<sup>2</sup>C-bus-compatible serial interface, the device that is expected to respond must be addressed first. The first byte sent after the START (S) condition is the address byte or 7bit slave ID. The MAX6917 acts as a slave transmitter/receiver. Therefore, SCL is only an input clock signal and SDA is a bidirectional data line. The slave address for the MAX6917 is shown in Figure 7.

### Address/Command Byte

The second byte of data sent after the START condition is the address/command byte (Figure 8). Each data transfer is initiated by an address/command byte. Bits 7–1 specify the designated register or RAM location to be read or written to, and the LSB (bit 0) specifies a write operation if logic zero or a read operation if logic one. The command byte is always input starting with the MSB (bit 7).

### Reading from the Timekeeping Registers

The timekeeping registers (seconds, minutes, hours, date, month, day, and year) and the control register can be read either with a single read or a burst read (Figure 9). Since the RTC runs continuously and a read takes a finite amount of time, there is the possibility that the clock counters could change during a read operation, thereby reporting inaccurate timekeeping data. In the MAX6917, each clock counter's data is buffered by a latch. Clock counter data is latched by the I<sup>2</sup>C bus read command (on the falling edge of SCL when the slave acknowledge bit is sent, after the address/command byte has been sent by the master to read a timekeeping register). Collision-detection circuitry ensures that this does not happen coincident with a seconds counter update to ensure accurate time data is being read. This avoids time-data changes during a read operation. The clock counters continue to count and keep accurate time during the read operation.

Figure 3. I<sup>2</sup>C System Configuration

Figure 4. START and STOP Conditions

If single reads are used to read each of the timekeeping registers individually, then it is necessary to do some error checking on the receiving end. An error can occur when the seconds counter increments before all the other registers are read out. For example, suppose a carry of 13:59:59 to 14:00:00 occurs during singleread operations of the timekeeping registers. Then the net data could become 14:59:59, which is erroneous real-time data. To prevent this with single-read operations, read the seconds register first (initial seconds) and store this value for future comparison. When the remaining timekeeping registers have been read out, read the seconds register again (final seconds). If the initial seconds value is 59, check that the final-seconds value is still 59; if not, repeat the entire single-read process for the timekeeping registers. A comparison of the initial-seconds value with the final-seconds value can indicate if there was a bus-delay problem in reading the timekeeping data (difference should always be 1s or less). Using a 100kHz bus speed, and sequential single reads, it would take under 2.5ms to read all seven of the timekeeping registers plus a second read of the seconds register.

The most accurate way to read the timekeeping registers is to perform a burst read. With burst reads, the main timekeeping registers (seconds, minutes, hours, date, month, day, year) and the control register are read sequentially, in the order listed with the seconds register first. They must be all read out as a group of

Figure 5. Bit Transfer

Figure 6. Acknowledge

Figure 7. MAX6917 Slave Address

eight registers, with 8 bytes each, for proper execution of the burst-read function. All seven timekeeping registers are latched upon the receipt of the burst-read command. The worst-case error that can occur between the actual time and the read time is 1s.

#### Writing to the Timekeeping Registers

The time and date can be set by writing to the timekeeping registers (seconds, minutes, hours, date, month, day, year, and century). To avoid changing the

Figure 8. Address/Command Byte

Figure 9. Read and Write Operations

**MAX6917**

current time by an incomplete write operation, the current time value is buffered from being written directly to the clock counters. The new data sent replaces the current contents of this input buffer. This time update data is loaded into the clock counters after the stop bit at the end of the I<sup>2</sup>C bus write operation. Collision-detection circuitry ensures that this does not happen coincident with a seconds-counter update to guarantee that accurate time data is being written. This avoids time data changes during a write operation. An incomplete write operation aborts the time-update procedures and the contents of the input buffer are discarded. The clock counters reflect the new time data beginning with the first 1s clock cycle after the stop bit. The clock counter is reset immediately after a write to the seconds register or a burst write to the timekeeping registers. This ensures that 1s clock tick is synchronous to timekeeping writes.

If single-write operations (Figure 9) are used to write to each of the timekeeping registers, then error checking is needed. If the seconds register is the one to be updated, update it first and then read it back and store its value as the initial seconds. Update the remaining timekeeping registers and then read the seconds register again (final seconds). If initial seconds was 59, ensure it is still 59. If initial seconds was not 59, ensure that final seconds is within 1s of initial seconds. If the seconds register is not to be written to, then read the seconds register first and save it as initial seconds. Write to the required timekeeping registers and then read the seconds register again (final seconds). If initial seconds was 59, ensure it is still 59. If initial seconds was not 59, ensure that final seconds is within 1s of initial seconds.

Although both single writes and burst writes are possible, the most accurate way to write to the timekeeping counters is to do a burst write (Figure 9). In the burst write, the main timekeeping registers (seconds, minutes, hours, date, month, day, year) and the control register are written sequentially. They must be all written to as a group of eight registers, with 8 bytes each, for proper execution of the burst-write function. All seven timekeeping registers and the control register are simultaneously loaded into the input buffer at the end of the 2-wire bus write operation. The worst-case error that can occur between the actual time and the write time update is 1s.

To avoid rollover issues when writing time data to the MAX6917, the remaining time and date registers must be written within 1s of updating the seconds register when using single writes. For burst writes, all eight registers must be written within this period (1s).

The weekday data in the day register increments at midnight. Values that correspond to the day of the week are user defined, but must be sequential (i.e., if 1 equals Sunday, then 2 equals Monday, and so on). If invalid values are written to the timekeeping registers, the operation becomes undefined.

#### **Timeout Feature**

The purpose of the bus timeout feature is to reset the serial bus interface and change the SDA line of the MAX6917 from an output to an input, which puts the SDA line into a high-impedance state. This is necessary when the MAX6917 is transmitting data and becomes stuck at a logic-low level. If the SDA line is stuck low, any other device on the bus is not able to communicate.

The timeout feature looks for a valid START and STOP condition to determine whether SDA has been stuck low. A valid START condition initiates the timeout counter in reference to the internal 1Hz clock. Counting begins on the first rising edge of the 1Hz clock after a valid START condition. If a valid STOP condition is detected before the next rising edge of the 1Hz clock, the timeout counter is stopped and awaits a new valid START condition. If a valid STOP condition is not detected before the next rising edge of the 1Hz clock, the I<sup>2</sup>C interface resets to the idle state and waits for a new I<sup>2</sup>C transaction. Depending on the occurrence of the START condition, that initiates the timeout counter, in reference to the internal 1Hz clock, the timeout period can be 1s to 2s. The lower limit of the timeout period (1s) imposes a limit on the SCL frequency of the MAX6917 because a burst read/write requires up to 96 bytes of information to be transmitted in between a START and STOP condition.

#### Registers

Tables 1 and 2 show the register map, as well as the register descriptions for the MAX6917.

#### **Control Register**

The control register contains bits for configuring the MAX6917 for custom applications. Bit D0 (BATT ON BLINK) and D1 (BATT LO BLINK) are used to enable a 1Hz blink rate on BATT\_ON and BATT\_LO when they are active; see the Battery Test section for details. D2 (WD TIME) and D3 (WD EN) are used to enable the watchdog function and select its timeout. For details, see the Watchdog Input section. D5 (INT/EXT TEST) sets whether the internal resistor ratio or an external resistor ratio is to be used to check for the low-battery condition; see the Battery Test section for details. D6 (XTAL EN) enables the crystal-fail-detect circuitry when set. See the Crystal-Fail Detect section for details. D7 (WP) is the write protect bit. Before any write operation to the registers (except the control register) or RAM, bit 7 must be zero. When set to one, the write-protect bit prevents write operations to any register (except the control register) or RAM location.

### Timekeeping and Alarm Thresholds Registers

Time and date data is stored in the timekeeping and alarm threshold registers in BCD format as shown in Table 1. The weekday data in the day register is user defined (a common format is 1 =Sunday, 2 = Monday, etc.)

#### AM/PM and 12hr/24hr Mode

For both timekeeping and alarm threshold registers (Table 1), D7 of the hours register is defined as the 12hr or 24hr mode-select bit. When set to one, the 12hr mode is selected. In the 12hr mode, D5 is the  $\overline{AM}/PM$  bit with logic one being PM. In the 24hr mode, D5 is the second 10hr bit (20hr to 23hr).

#### Clock-Burst Mode

Addressing the clock-burst register specifies burstmode operation. In this mode, the first eight clock/calendar registers (seven timekeeping and the control register) can be consecutively read or written to by using the address/command byte 00h for a write or 01h for a read (Table 1). If the write-protect bit is set to one when a write-clock/calendar-burst mode is specified, no data transfer occurs to any of the seven timekeeping registers or the control register. When writing to the clock/calendar registers in the burst mode, the first eight registers must be written to for the data to be transferred.

#### RAM

The static RAM consists of 96 x 8 bits addressed consecutively in the RAM address/command space. Even address/commands (3Eh to FCh) are used for RAM writes and odd address/commands (3Fh to FDh) are used for RAM reads (Table 2).

#### **RAM-Burst Mode**

Sending the RAM-burst address/command (FEh for write, FFh for read) specifies burst-mode operation. In this mode, the 96 RAM locations can be consecutively read or written to starting with bit 7 of address/command 3Eh for writes, and 3Fh for reads. A burst read outputs all 96 bytes of RAM. When writing to RAM in burst mode, it is not necessary to write all 96 bytes for the data to transfer; each complete byte written is transferred to the RAM. When reading from RAM, data are output until all 96 bytes have been read, or until the data transfer is stopped by the I<sup>2</sup>C master.

#### Status Register

The status register contains individual bits for monitoring the status of several functions of the MAX6917. Bits D0–D3 are unused and always read zero (Table 1). D4 (ALM OUT) reflects the state of the alarm function; see the *Alarm-Generation Function* section for details. D5 (BATT LO) indicates the state of the battery connected to V<sub>BATT</sub>; see the *Battery Test* section for more information. D6 (DATA VALID) alerts the user if all power was lost. See the *Data Valid Bit* section for details. D7 (XTAL FAIL) is the output of the crystal-fail detect circuit. See the *Crystal-Fail Detect* section for details.

## Table 1. Register Map

**MAX6917**

| REGISTER ADDRESS      |    |          |    |            |    |    |    |        | REGISTER FUNCTION         |                          |                 |                            |                          |        |       |            |            |

|-----------------------|----|----------|----|------------|----|----|----|--------|---------------------------|--------------------------|-----------------|----------------------------|--------------------------|--------|-------|------------|------------|

| FUNCTION              | A7 | A6       | A5 | <b>A</b> 4 | A3 | A2 | A1 | A0     | VALUE                     | D7                       | D6              | D5                         | D4                       | D3     | D2    | D1         | D0         |

| CLOCK<br>BURST        | 0  | 0        | 0  | 0          | 0  | 0  | 0  | R<br>W |                           |                          |                 |                            |                          |        |       |            |            |

| SEC                   | 1  | 0        | 0  | 0          | 0  | 0  | 0  | R      | 0–59                      | 0                        |                 | 10 SEC                     |                          |        | 1 S   | C          |            |

| 3LU                   |    | 0        | 0  | 0          | 0  | 0  | 0  | W      | POR STATE                 | 0                        | 0               | 0                          | 0                        | 0      | 0     | 0          | 0          |

|                       |    |          |    |            |    |    |    | R      | 0–59                      | 0                        |                 | 10 MIN                     |                          |        | 1 N   | 1IN        |            |

| MIN                   | 0  | 1        | 0  | 0          | 0  | 0  | 0  | W      | POR STATE                 | 0                        | 0               | 0                          | 0                        | 0      | 0     | 0          | 0          |

|                       |    |          |    |            |    |    |    | R      | 00.00                     |                          | 1               | 10.110                     |                          |        |       |            |            |

| HR                    | 1  | 1        | 0  | 0          | 0  | 0  | 0  | W      | 00-23                     | 12/24                    | 0               | 10 HR<br>AM/               | 10 HR                    |        | 11    | IR         |            |

|                       |    |          |    |            |    |    |    |        | 01–12                     |                          |                 | PM                         |                          |        |       |            |            |

|                       |    |          |    |            |    |    |    |        | POR STATE                 | 0                        | 0               | 0                          | 0                        | 0      | 0     | 0          | 0          |

|                       |    |          |    |            |    |    |    | R      | 01–28/29<br>01–30/31      | 0                        | 0               | 10 DA                      | ATF                      |        | 1 D.4 | TF         |            |

| DATE                  | 0  | 0        | 1  | 0          | 0  | 0  | 0  | W      | POR STATE                 | 0                        | 0               | 0                          | 0                        | 0      | 0     | 0          | 1          |

|                       |    |          |    |            |    |    |    | R      | 01–12                     | 0                        | 0               | 0                          | 10 M                     |        | 1 M0  | NTH        |            |

| MONTH                 | 1  | 0        | 1  | 0          | 0  | 0  | 0  | W      | POR STATE                 | 0                        | 0               | 0                          | 0                        | 0      | 0     | 0          | 1          |